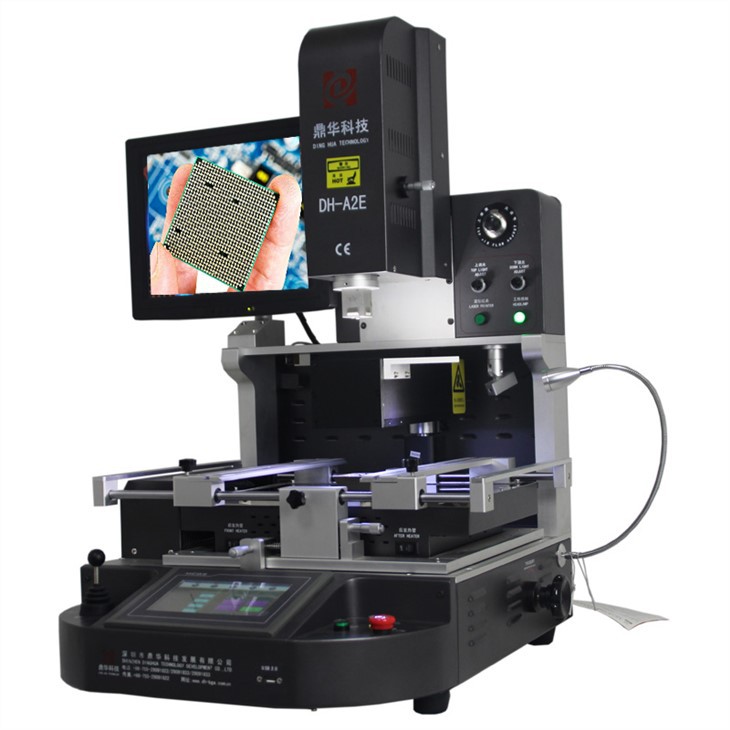

محطة إعادة العمل Auto Optical BGA

تستخدم على نطاق واسع في إصلاح مستوى الرقاقة للوحة الأم للهاتف المحمول والكمبيوتر المحمول والكمبيوتر والتلفزيون ومكيفات الهواء وما إلى ذلك. وتتميز بمعدل نجاح عالٍ في الإصلاح ودرجة عالية من الأتمتة وتوفر الكثير من الجهود البشرية. نحن مصنعون محترفون لهذا الجهاز ولدينا هذه الآلات متوفرة في المخزون.

الوصف

محطة إعادة العمل Auto Optical BGA

1. تطبيق محطة إعادة العمل البصري التلقائي BGA

اللوحة الأم للكمبيوتر والهاتف الذكي والكمبيوتر المحمول ولوحة منطق MacBook والكاميرا الرقمية ومكيف الهواء والتلفزيون وغيرها من الأجهزة الإلكترونية

المعدات من الصناعة الطبية ، وصناعة الاتصالات ، وصناعة السيارات ، إلخ.

مناسبة لأنواع مختلفة من الرقائق: BGA ، PGA ، POP ، BQFP ، QFN ، SOT223 ، PLCC ، TQFP ، TDFN ، TSOP ، PBGA ، CPGA ، رقاقة LED.

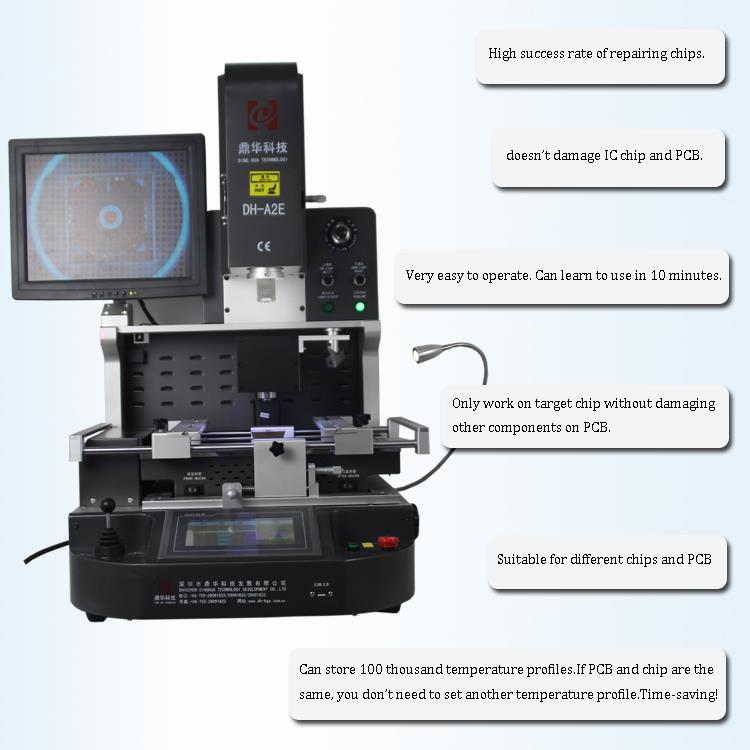

2. ميزات المنتج لمحطة إعادة العمل البصري BGA الأوتوماتيكية

• معدل نجاح عالٍ للإصلاح على مستوى الرقاقة. عملية إزالة اللحام والتركيب واللحام تلقائية.

• يمكن ضمان المحاذاة الدقيقة لكل وصلة لحام باستخدام كاميرا CCD للمحاذاة البصرية.

• يمكن ضمان التحكم الدقيق في درجة الحرارة من خلال 3 مناطق تسخين مستقلة. يمكن للآلة ضبط وحفظ

1 مليون ملف تعريف درجة الحرارة.

• بناء في فراغ في رأس التركيب ، تلتقط شريحة BGA تلقائيًا بعد اكتمال عملية إزالة اللحام.

3.Specification من السيارات البصرية BGA محطة إعادة العمل

4.Details من Auto Optical BGA Rework Station

كاميرا CCD (نظام محاذاة بصرية دقيقة) ؛ 2. hd العرض الرقمي. 3. ميكرومتر (ضبط زاوية الرقاقة)؛

4.3 سخانات مستقلة (الهواء الساخن والأشعة تحت الحمراء) ؛ 5. تحديد المواقع بالليزر. 6. واجهة شاشة تعمل باللمس HD ، تحكم PLC.

7.Led كشافات. 8. التحكم بعصا التحكم.

5.لماذا تختار محطة إعادة العمل البصري BGA الأوتوماتيكية الخاصة بنا؟

6. شهادة محطة إعادة العمل البصري التلقائي BGA

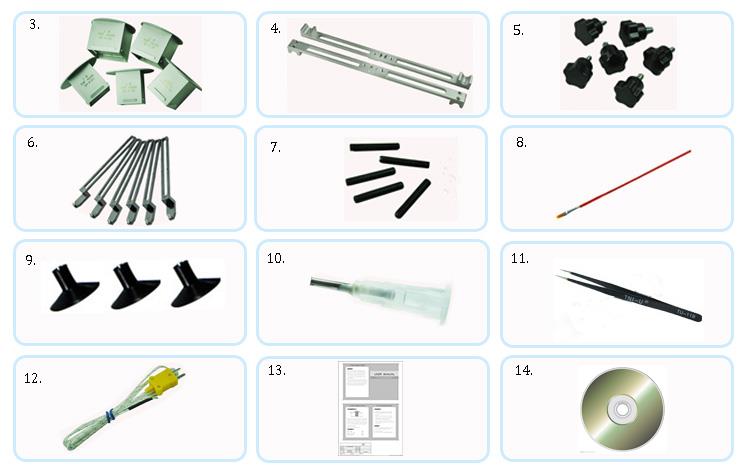

7.التعبئة والشحن لمحطة إعادة العمل البصري BGA الأوتوماتيكية

8. التعليمات

كيف تختبر الرقاقة؟

الاختبار الأولي للرقاقة على مستوى النظام

تعتمد SoC على عمليات فرعية عميقة ، لذا يتطلب اختبار أجهزة Soc الجديدة نهجًا جديدًا تمامًا. لأن كل مكون وظيفي

متطلبات الاختبار الخاصة به ، يجب على مهندس التصميم وضع خطة اختبار في وقت مبكر من عملية التصميم.

يجب تنفيذ خطة اختبار كتلة تلو كتلة لأجهزة SoC: أدوات ATPG المكونة بشكل صحيح لاختبار المنطق ؛ أوقات اختبار قصيرة جديد عالي السرعة

نماذج خطأ وذاكرة متعددة أو اختبارات مجموعة صغيرة. بالنسبة لخط الإنتاج ، لا تكتشف طريقة التشخيص الخطأ فحسب ، بل تفصل أيضًا

عقدة خاطئة من عقدة العمل. بالإضافة إلى ذلك ، يجب استخدام تقنيات مضاعفة الاختبار كلما أمكن ذلك لتوفير وقت الاختبار. في مجال عالي

يتميز اختبار IC المتكامل وتقنيات التصميم القابلة للاختبار ATPG و IDDQ بآلية قوية لفصل الأعطال.

تتضمن المعلمات الفعلية الأخرى التي يجب التخطيط لها مسبقًا عدد المسامير التي يجب مسحها ضوئيًا ومقدار الذاكرة في كل طرف دبوس.

يمكن تضمين عمليات مسح الحدود في SoC ، ولكنها لا تقتصر على اختبارات التوصيل البيني على اللوحات أو الوحدات النمطية متعددة الشرائح.

على الرغم من أن حجم الرقاقة آخذ في التناقص ، لا يزال بإمكان الشريحة تجميع الملايين إلى 100 مليون ترانزستور ، وزاد عدد أوضاع الاختبار إلى مستوى غير مسبوق

مستويات ، مما يؤدي إلى دورات اختبار أطول. يمكن اختبار هذه المشكلة. ضغط الوضع لحلها ، يمكن أن تصل نسبة الضغط إلى 20 في المائة إلى 60 في المائة. على نطاق واسع اليوم

تصميم الرقاقة ، لتجنب مشاكل السعة ، من الضروري العثور على برنامج اختبار يمكن تشغيله على أنظمة تشغيل 64- بت.

بالإضافة إلى ذلك ، يواجه برنامج الاختبار مشكلات اختبار جديدة ناجمة عن عمليات شبه ميكرون عميقة وتكرار متزايد. في الماضي ، كان وضع اختبار ATPG لـ

اختبار أخطاء الحجب الثابت لم يعد قابلاً للتطبيق. أدت إضافة أنماط وظيفية إلى الأدوات التقليدية إلى صعوبة العثور على أخطاء جديدة. أفضل نهج هو

صنف مجموعات الوضع الوظيفي السابقة لتحديد الأخطاء التي لا يمكن اكتشافها ، ثم قم بإنشاء وضع ATPG لالتقاط أنواع الأخطاء المفقودة هذه.

مع زيادة سعة التصميم وانخفاض وقت الاختبار لكل ترانزستور ، من أجل العثور على المشاكل المتعلقة بالسرعة والتحقق من توقيت الدائرة ، وهي طريقة اختبار متزامنة

يجب أن يتم توظيفه. يجب أن يشتمل الاختبار المتزامن على نماذج أخطاء متعددة ، بما في ذلك النماذج العابرة وتأخيرات المسار و IDDQ.

تعتقد بعض الشركات في الصناعة أن الجمع بين أخطاء الحجب والوظيفية والعابرة / تأخير المسار قد يكون استراتيجية الاختبار الأكثر فعالية. لعمق

تعتبر الرقائق الفرعية الميكرونية والتشغيل عالي التردد والاختبار العابر وتأخير المسار أكثر أهمية.

لحل مشكلة دقة ATE عند مزامنة مركز الاختبار وتقليل التكلفة ، من الضروري إيجاد طريقة جديدة تبسط واجهة

جهاز الاختبار (يتطلب اختبار التأخير العابر والمسار ساعة دقيقة في واجهة جهاز الاختبار) ، فهو يضمن أن الإشارة دقيقة بدرجة كافية أثناء الاختبار.

نظرًا لوجود احتمال كبير لحدوث عيوب تصنيعية في كتلة ذاكرة SoC ، يجب أن يكون لذاكرة BIST وظيفة تشخيصية. بمجرد العثور على مشكلة ،

يمكن تعيين وحدة العنوان المعيبة على الذاكرة الزائدة لوحدة العنوان الاحتياطية ، وسيتم تجاهل عنوان الخطأ المكتشف. تجنب التخلص منه

الشريحة باهظة الثمن بالكامل.

يؤدي اختبار كتل الذاكرة المدمجة الصغيرة إلى التخلص من الحاجة إلى بوابات إضافية أو منطق تحكم. على سبيل المثال ، يمكن أن تقوم تقنيات اختبار تحويل المتجهات بالتحويل

أوضاع وظيفية في سلسلة من أوضاع المسح.

على عكس طريقة BIST ، لا يتطلب الإدخال الوظيفي لكتلة الذاكرة الالتفافية منطقًا إضافيًا. نظرًا لعدم وجود منطق اختبار إضافي مطلوب ، فإن SoC

يمكن لمهندسي التطوير إعادة استخدام أنماط الاختبار التي تم تشكيلها في الماضي.

لا تختبر أدوات ATPG المتقدمة وحدات الماكرو بالتوازي فحسب ، بل تحدد أيضًا ما إذا كانت هناك تعارضات ، بالإضافة إلى تفصيل وحدات الماكرو التي يمكن اختبارها بشكل متوازٍ وأيها

لا يمكن اختبار وحدات الماكرو بالتوازي. بالإضافة إلى ذلك ، يمكن اختبار وحدات الماكرو هذه بشكل فعال حتى إذا كانت ساعة الماكرو هي نفسها ساعة المسح (مثل الذاكرة المتزامنة).

في الوقت الحالي ، لا توجد نقاط اختبار كافية على اللوحة ذات الوجهين الكثيفة ، ويجب أن تكون كل شريحة معقدة مزودة بدائرة مسح حدودية. بدون

عمليات فحص الحدود وعمليات البحث عن عيوب التصنيع على مستوى اللوحة صعبة للغاية ولا يمكن العثور عليها. مع مسح الحدود ، يكون الاختبار على مستوى اللوحة أمرًا سهلاً للغاية

ومستقلة عن الدوائر المنطقية داخل الشريحة. يمكن لمسح الحدود أيضًا تكوين وضع ATPG لسلسلة مسح الشريحة في أي مرحلة من مراحل الإنتاج.